# 86 GHz Static and 110 GHz Dynamic Frequency Dividers in SiGe Bipolar Technology

Herbert Knapp, Martin Wurzer, Thomas F. Meister, Klaus Aufinger,

Josef Böck, Sabine Boguth, Herbert Schäfer

Infineon Technologies AG,

Otto-Hahn-Ring 6, D-81730 Munich, Germany,

E-Mail: herbert.knapp@infineon.com

**Abstract** — We present static and dynamic frequency dividers manufactured in a 200 GHz  $f_T$  SiGe bipolar technology. The static divider has a divide ratio of 32 and operates up to 86.2 GHz. The dynamic divider is based on regenerative frequency division and has a divide ratio of two. It operates up to 110 GHz (limited by the measurement equipment). The power consumption of the static and dynamic frequency dividers is 900 mW and 310 mW, respectively.

## I. INTRODUCTION

Frequency dividers are used in a wide variety of applications and provide an important benchmark for the performance of high-speed technologies. Static frequency dividers using InP heterojunction bipolar transistors (HBTs) with maximum operating frequencies of 87 GHz [1] and 100 GHz [2] have been reported recently.

The fastest static frequency dividers in silicon germanium technology so far have achieved maximum operating frequencies of 71.8 GHz using conventional master-slave flip-flops [3] and 81 GHz using a pre-tracking technique [4].

The highest operating frequencies reported so far for dynamic dividers both in SiGe and III-V technologies are in the range of 90 GHz to 100 GHz. These dynamic frequency dividers are either based on clocked inverters [5] or on regenerative frequency division [6], [7], [8], [9].

In this paper we present a static and a dynamic frequency divider. Both circuits were designed to fully exploit the potential that advanced SiGe technologies offer for high-speed circuit design.

## II. CIRCUIT DESIGN

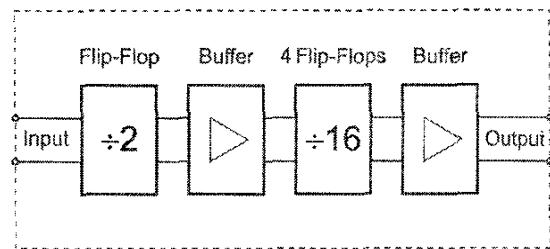

### A. Static Frequency Divider

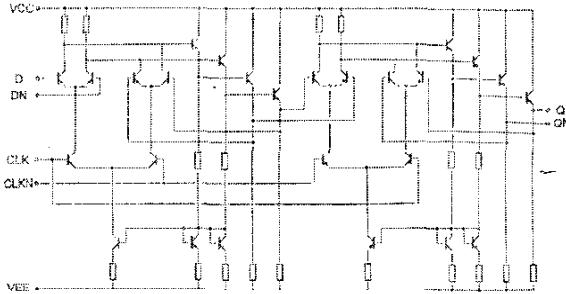

The static frequency divider has a divide ratio of 32 and consists of five master-slave flip-flops (figure 1). The input signal is applied to the first divider stage via a pair of emitter followers. Figure 2 shows the schematic diagram of the first master-slave stage which determines the maximum operating frequency of the frequency divider. This stage uses two cascaded emitter followers to achieve the highest possible operating frequency. The current of the first emitter follower stage is used as reference current in the current mirror which determines the tail current of the latch. This enables a highly symmetric and very compact layout. The transistors in the latch operate at a current density of 7 mA/ $\mu\text{m}^2$ .

Fig. 1. Static frequency divider block diagram

The first flip-flop is followed by a buffer consisting of a differential amplifier and emitter followers. By using small transistors at the buffer input the capacitive load to the flip-flop is kept small, leading only to a slight decrease of the maximum operating frequency of the first divider stage. Emitter followers at the buffer output provide the clock signal for the four-stage asynchronous divider.

The flip-flops in these four divider stages are sim-

Fig. 2. Master-slave flip-flop

ilar to figure 2 but use only single emitter followers to reduce power consumption.

The last divider stage is followed by an output buffer which is designed to provide an output voltage swing of  $> 2 \times 250 \text{ mV}_{pp}$  at an external  $50 \Omega$  load.

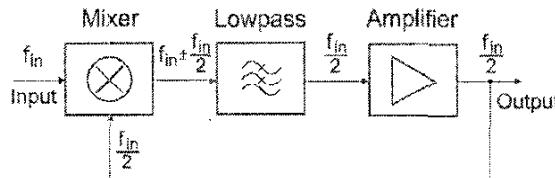

#### B. Dynamic Frequency Divider

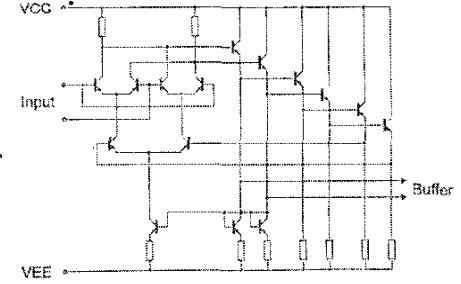

The dynamic frequency divider is based on the principle of regenerative frequency division. Figure 3 shows the block diagram. The input signal is applied to a mixer which is followed by a low-pass filter and an amplifier. The output signal is fed back to the second mixer input. When using an active mixer no separate amplifier is necessary. The frequency response of the mixer conversion gain shows low-pass behavior. Therefore no additional filter is required and the regenerative divider consists only of an active double-balanced mixer (figure 4). Three emitter follower stages are used in the feedback path of the mixer to obtain a high gain bandwidth. The output signal, which is then applied to a buffer amplifier, is taken from the first emitter follower stage. The two-stage buffer amplifier serves as limiter to make the output signal independent from the divider input amplitude.

Fig. 3. Regenerative frequency division

### III. TECHNOLOGY

The circuit is fabricated in an advanced SiGe bipolar process based on the technology presented in

Fig. 4. Regenerative frequency divider using an active mixer

[7]. It uses a double-polysilicon self-aligned emitter-base configuration with effective emitter width of  $0.15 \mu\text{m}$ . The SiGe:C base is grown by selective epitaxy. The maximum transit frequency  $f_T$  of the transistors is 200 GHz. The technology provides three types of polysilicon resistors and four layers of metalization.

Fig. 5 shows a chip photograph of the static frequency divider. The chip size, which is determined by the pad frame, is  $550 \mu\text{m} \times 450 \mu\text{m}$ .

Fig. 5. Chip photograph of the static frequency divider (size:  $550 \mu\text{m} \times 450 \mu\text{m}$ )

## IV. MEASUREMENT RESULTS

#### A. Static Frequency Divider

Measurements were performed on wafer with a single-ended input signal. The complementary input was left unconnected.

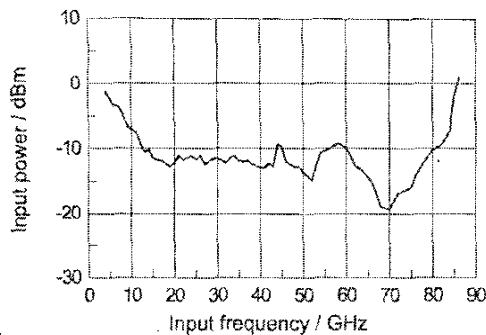

Operating with a supply voltage of  $-5 \text{ V}$  the static frequency divider consumes 180 mA. Figure 6 shows the measured input sensitivity. The circuit operates up to a maximum input frequency of

86.2 GHz. The low-frequency response is limited by the slew-rate of the sinusoidal input signal.

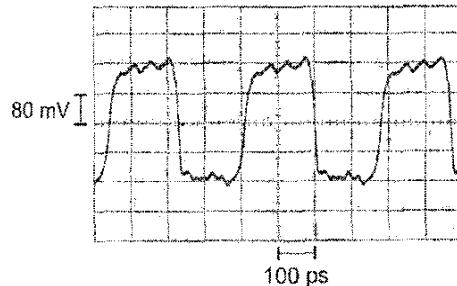

Figure 7 shows the single-ended output signal of the frequency divider at an input frequency of 86.2 GHz. The output voltage swing is larger than  $300 \text{ mV}_{pp}$ .

Fig. 6. Input sensitivity of the static frequency divider

Fig. 7. Single-ended output signal of the static frequency divider ( $f_{in} = 86.2 \text{ GHz}$ )

### B. Dynamic Frequency Divider

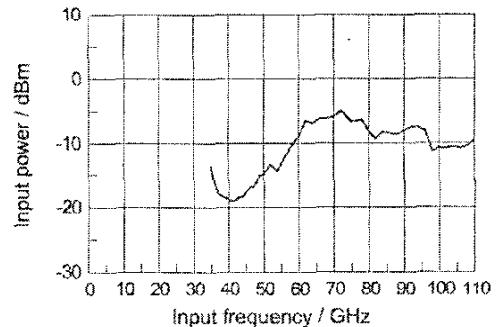

The dynamic frequency divider was measured on wafer using 1.0 mm coaxial probes. Input signals with frequencies up to 50 GHz were generated by a microwave generator while millimeter-wave source modules and waveguide-to-coax adapters were used at frequencies above 50 GHz. All measurements were performed with single-ended input signals. The complementary input was not connected. The output signal of the divider was applied to a frequency counter and to a spectrum analyzer.

The dynamic frequency divider operates with a supply voltage of  $-5 \text{ V}$  at a total supply current (including the output buffer) of 62 mA. Figure 8 shows the measured input sensitivity. The minimum oper-

ating frequency of the circuit is 35 GHz. The divider operates up to 110 GHz which is the highest frequency our measurement equipment provides. With a reduced supply voltage of  $-4.5 \text{ V}$  the circuit still operates up to 110 GHz while consuming only 225 mW.

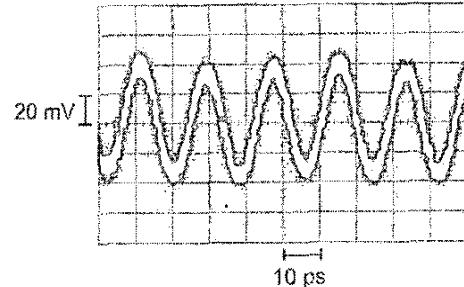

The single-ended output amplitude at 110 GHz input frequency is  $80 \text{ mV}_{pp}$  (fig. 9).

Fig. 8. Input sensitivity of the dynamic frequency divider

Fig. 9. Single-ended output signal of the dynamic frequency divider ( $f_{in} = 110 \text{ GHz}$ )

### V. CONCLUSIONS

We have presented static and dynamic frequency dividers in SiGe bipolar technology. The static divider operates up to 86.2 GHz which is the highest value published so far for silicon-based technologies.

The dynamic frequency divider is based on regenerative frequency division and operates between 35 GHz and 110 GHz (limited by the measurement setup). To the authors' knowledge this is the highest operating frequency reported so far for all IC technologies.

Table I gives a summary of the performance of the two circuits.

|                         | Static Frequency Divider       | Dynamic Frequency Divider      |

|-------------------------|--------------------------------|--------------------------------|

| Divide ratio            | 32                             | 2                              |

| Maximum input frequency | 86.2 GHz                       | $\geq 110$ GHz                 |

| Supply voltage          | -5.0 V                         | -5.0 V                         |

| Supply current          | 180 mA                         | 62 mA                          |

| Chip size               | $550 \times 450 \mu\text{m}^2$ | $550 \times 450 \mu\text{m}^2$ |

| Technology              | 200 GHz $f_T$ SiGe bipolar     |                                |

TABLE I. Frequency divider data

#### REFERENCES

- [1] S. Krishnan, Z. Griffith, M. Urteaga, Y. Wei, D. Scott, N. Dahlstrom, N. Parthasarathy, and M. Rodwell, "87 GHz Static Frequency Divider in an InP-based Mesa DHBT Technology," *GaAs IC Symposium Digest*, Oct. 2002, pp. 294–296.

- [2] M. Mokhtari, C. Fields, and R. D. Rajavel, "100+GHz Static Divide-By-2 Circuit in InP-DHBT Technology," *GaAs IC Symposium Digest*, Oct. 2002, pp. 291–294.

- [3] M. Wurzer, J. Böck, H. Knapp, K. Aufinger, and T. F. Meister, "71.8 GHz Static Frequency Divider in a SiGe Bipolar Technology," *Bipolar/BiCMOS Circuits and Technology Meeting*, Sept. 2002, pp. 216–219.

- [4] K. Washio, E. Ohue, R. Hayami, A. Kodama, H. Shimamoto, M. Miura, K. Oda, I. Suzumura, T. Tominari, and T. Hashimoto, "Ultra-High-Speed Scaled-down Self-aligned SEG SiGe HBTs," *International Electron Devices Meeting (IEDM)*, Dec. 2002, pp. 767–770.

- [5] S. Tsunashima, H. Nakajima, E. Sano, M. Ida, K. Kurishima, N. Watanabe, T. Enoki, and H. Sugahara, "90-GHz operation of a novel dynamic frequency divider using InP/InGaAs HBTs," *Indium Phosphide and Related Materials Conference (IPRM)*, May 2002, pp. 43–46.

- [6] K. Washio, E. Ohue, K. Oda, R. Hayami, M. Tanabe, and H. Shimamoto, "Optimization of Characteristics Related to the Emitter-Base Junction in Self-Aligned SEG SiGe HBTs and Their Application in 72-GHz-Static/92-GHz-Dynamic Frequency Dividers," *IEEE Transactions on Electron Devices*, vol. 49, no. 10, pp. 1755–1760, Oct. 2002.

- [7] J. Böck, H. Schäfer, H. Knapp, D. Zöschg, K. Aufinger, M. Wurzer, S. Boguth, M. Rest, R. Schreiter, R. Stengl, and T. F. Meister, "Sub 5 ps SiGe Bipolar Technology," *International Electron Devices Meeting (IEDM)*, Dec. 2002, pp. 763–766.

- [8] A. Rylyakov, A. Klapproth, B. Jagannathan, and G. Freeman, "100 GHz dynamic frequency divider in SiGe bipolar technology," *Electronics Letters*, vol. 39, no. 2, pp. 217–218, Jan. 2003.

- [9] S. Kudsuz, W. W. Haydl, M. Neumann, and M. Schlechtweg, "94/47-GHz Regenerative Frequency Divider MMIC with Low Conversion Loss," *IEEE Journal of Solid State Circuits*, vol. 35, no. 9, pp. 1312–1317, Sept. 2000.